# Heteroepitaxial Growth of Gold Nanostructures on Silicon by Galvanic Displacement

Sayed Y. Sayed,<sup>†,‡</sup> Feng Wang,<sup>†,§</sup> Marek Malac,<sup>†,§</sup> Al Meldrum,<sup>§</sup> Ray F. Egerton,<sup>†,§</sup> and Jillian M. Buriak<sup>†,‡,</sup>\*

<sup>†</sup>National Institute for Nanotechnology, National Research Council, 11421 Saskatchewan Drive, Edmonton T6G 2M9, Canada, <sup>‡</sup>Department of Chemistry, University of Alberta, Edmonton T6G 2G7, Canada, and <sup>§</sup>Department of Physics, University of Alberta, Edmonton T6G 2G7, Canada

nterfacing metals with semiconductor surfaces at the nanometer scale has received much attention<sup>1</sup> as a result of the critical importance of these interfaces for applications such as integrated circuits,<sup>2-4</sup> optoelectronics,<sup>5,6</sup> and others.<sup>7,8</sup> An efficient and versatile approach for the synthesis of metallic nanostructures on semiconductors is galvanic displacement, a spontaneous electrochemical reaction that is a member of the electroless deposition family.9-51 In this class of reactions, sufficiently oxidizing metal ions, with a redox potential more positive than that of substrate, are reduced by electrons derived from the bonding electrons of the substrate lattice valence band; the reaction is accompanied by substrate dissolution and occurs in the absence of an external source of electric current or chemical reducing agents.<sup>42</sup> The result is metallic nanoparticles and films interfaced directly with the substrate surface.<sup>13,42</sup> Because the reaction is carried out at room temperature with the simplest of chemical apparatus (water, metal ion, substrate in a beaker), it is straightforward to carry out and is less expensive and faster than commonly used metal evaporation<sup>52,53</sup> and sputtering techniques.5,54

Galvanic displacement has seen application in a number of different areas, particularly those related to the construction of nanoscale metallic and semiconductor architectures. For instance, Carraro and coworkers used galvanic displacement to produce gold nanoparticle catalyst arrays in silicon trenches for the synthesis of horizontally suspended silicon nanowires (NWs).<sup>11</sup> Gösele and co-workers demonstrated that gold nanoparticles on silicon surfaces, prepared *via* galvanic displacement, resulted in the growth of a high quantity of epitaxial **ABSTRACT** This work focuses on the synthesis and interfacial characterization of gold nanostructures on silicon surfaces, including Si(111), Si(100), and Si nanowires. The synthetic approach uses galvanic displacement, a type of electroless deposition that takes place in an efficient manner under aqueous, room-temperature conditions. The case of gold-on-silicon has been widely studied and used for several applications and yet, a number of important, fundamental questions remain as to the nature of the interface. Some studies are suggestive of heteroepitaxial growth of gold on the silicon surface, whereas others point to the existence of a silicon—gold intermetallic sandwiched between the metallic gold and the underlying silicon substrate. Through detailed high resolution transmission electron microscopy (TEM), combined with selected area electron diffraction (SAED) and nanobeam diffraction (NBD), heteroepitaxial gold that is grown by galvanic displacement is confirmed on both Si(100) and Si(111), as well as silicon nanowires. The coincident site lattice (CSL) of gold-on-silicon results in a very small 0.2% lattice mismatch due to the coincidence of four gold lattices to three of silicon. The presence of gold—silicon interfaces appear heterogeneous with distinct areas of heteroepitaxial gold on silicon, and others, less well-defined, where intermetallics may reside. The high resolution cross-sectional TEM images reveal a roughened silicon interface under these aqueous galvanic displacement conditions, which most likely promotes nucleation of metallic gold islands that merge over time: a Volmer—Weber growth mechanism in the initial stages.

**KEYWORDS:** gold nanoparticles  $\cdot$  silicon surfaces  $\cdot$  silicon nanowires  $\cdot$  electron microscopy  $\cdot$  galvanic displacement  $\cdot$  heteroepitaxy  $\cdot$  intermetallics

Si nanowires with neat and sharp crystallographic interfaces, whereas evaporated gold films led to low amounts of epitaxial nanowires, with defects at the silicon nanowire-bulk silicon interface.55,56 The group of Kamins and co-workers from Hewlett-Packard (HP) demonstrated galvanic displacement directly on silicon nanowires to produce gold nanoparticledecorated silicon nanostructures.<sup>49</sup> Galvanic displacement has also been found to be amenable to nanoscale patterning via self-assembled block copolymer templates, reverse micelle deposition on surfaces, and dip-pen nanolithography (DPN) to produce, in a controlled manner, metallic nanostructures on a variety of different semiconductor interfaces.<sup>11,17,32,57</sup> In a completely unrelated application, galvanic displacement

\*Address correspondence to jburiak@ualberta.ca

Received for review June 26, 2009 and accepted August 21, 2009.

Published online August 31, 2009. 10.1021/nn900685a CCC: \$40.75

© 2009 American Chemical Society

**RTICLE**

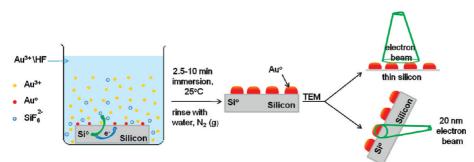

Figure 1. A silicon substrate is immersed in a mixture of a gold salt, [KAuCl<sub>4</sub> (aq) and HF (aq)] at room temperature. Galvanic displacement occurs when the semiconductor surface acts as the electron source for the reduction of the metal salt. HF (aq) is required to ensure the formation of soluble SiF<sub>6</sub><sup>2-</sup>(aq) and related species from the resulting oxidized silicon to allow for continued electron transfer. Transmission electron microscope (TEM) investigations were then carried out on backside thinned planar and cross-sectioned samples.

of silver nanoparticles on silicon can be used to etch silicon nanowire arrays in a wet chemical fashion.<sup>58</sup>

Although gold-on-silicon nanostructures, prepared by galvanic displacement, have been used in the fabrication of many device architectures, the Au-Si interface is not well understood, and is the source of much interest. A detailed understanding of the nature and the structure of the gold-silicon interface as prepared by galvanic displacement, and the subsequent growth mode of the gold nanostructures merits detailed consideration not only from a technological perspective, but also to elucidate fundamentals in interfacial nanoscience.<sup>11,32,44,45</sup> In terms of galvanic displacement of metals on semiconductors, a number of basic guestions remain that do not yet allow for a convergent set of conclusions to be made as to the nature of these interfaces. For instance in the case of gold on silicon, XPS depth profiling clearly indicates evidence for the existence of undefined interfacial gold-silicon intermetallics,<sup>10</sup> whereas surface X-ray diffraction studies point to heteroepitaxial growth of gold on silicon;<sup>46</sup> the relationship or connection between the presence of intermetallics and heteroepitaxy is difficult to envisage. In addition to questions regarding the growth mechanism of metallic nanoparticles on semiconductors via galvanic displacement, both Volmer-Weber<sup>37,38,46,47</sup> and Stranski-Krastanov modes<sup>48</sup> of growth have been suggested. To attempt to answer some of these questions, we harnessed the precision of transmission electron microscopy (TEM) nanobeam diffraction analyses to characterize, in detail, the nature of gold-silicon interfaces formed via galvanic displacement on flat single crystal Si(111) and Si(100) surfaces, and silicon nanowires.

### **RESULTS AND DISCUSSION**

The synthesis of gold nanostructures on silicon surfaces was carried out through immersion of a semiconductor wafer in a solution of metal ions with a sufficiently high oxidation potential; this reaction, galvanic displacement, occurs spontaneously as outlined in Figure 1. The reaction is essentially a corrosion reaction in conjunction with metal deposition—the semiconductor acts as a source of electrons that reduce the metal ions in solution to M(0) on the surface, while surface atoms are oxidized and solubilized either locally and/or distally, from an exposed surface.13,18,42 In the case of silicon, hydrofluoric acid is required to ensure continuous metallic growth since the spontaneously formed silicon oxide product is a dielectric, and would prevent further metal ion reduction. In the presence of HF (aq), the silicon ox-

ide layer is dissolved in situ to form soluble  ${\rm SiF_6}^{2-}$  (aq) species according to eq 1:<sup>28</sup>

Si + 6F<sup>-</sup>

$$\rightarrow$$

SiF<sub>6</sub><sup>2-</sup> + 4e<sup>-</sup>  $E^{\circ}_{SiF_6^{2-}/Si} =$

-1.2 V vs NHE (1)

AuCl<sub>4</sub><sup>-</sup> + 3e<sup>-</sup>  $\rightarrow$  Au°(s) + 4Cl<sup>-</sup>  $E^{\circ}_{Au^{3+}/Au^{\circ}} =$

+1.42 V vs NHE (2)

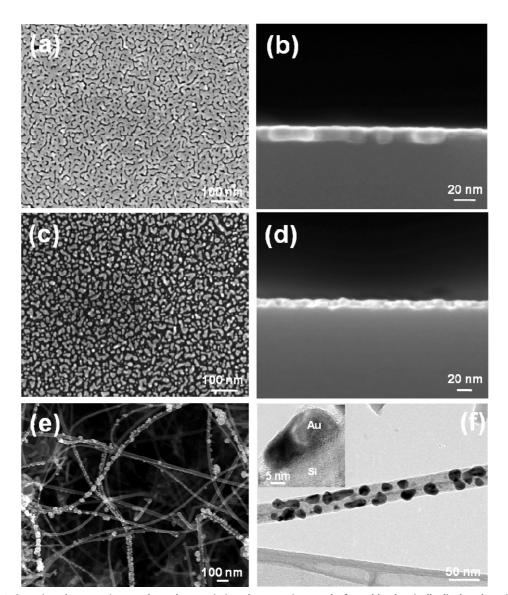

Figure 2 shows the formation of nanostructured gold films on single crystal shards of Si(111) and Si(100), and silicon nanowires, by immersion in dilute KAuCl<sub>4</sub> (aq) and HF (aq) for short periods of time (seconds to minutes). Plan view (top view) SEM images reveal more continuous growth of gold on Si(111) as opposed to Si(100), but cross-section SEM images show no appreciable difference in the thickness of the gold layer, ~10 nm in each case. On silicon nanowires, gold nanoparticles of different sizes (20-30 nm) are observed. Longer immersion times results in greater quantities of metallic deposition on all of the silicon surfaces studied, as expected (Supporting Information).<sup>14,49</sup>

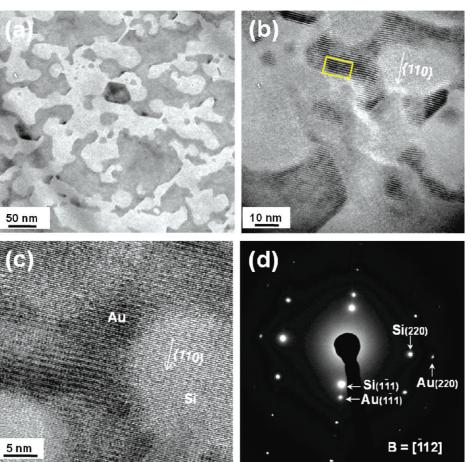

Heteroepitaxial Growth of Gold Nanoparticles on Silicon Surfaces. To characterize the structure and morphology of the gold nanoparticle layer topping the silicon, the substrates were characterized by high resolution transmission electron microscopy (HRTEM) and electron diffraction (beam size ca. 20-100 nm). To carry out TEM, the flat hydrogen-terminated silicon surfaces (500 µmthick wafer shards) were immersed in a 0.1 mM KAuCl<sub>4</sub> (aq) and 1% HF (aq) solution for 2.5 min, and then the backside of the silicon shard was mechanically polished until the silicon was thinned to less than a micrometer to permit TEM imaging. Shorter immersion times were used to ensure a thin gold layer appropriate for plan view TEM (2.5 min versus 7.5 min). Figure 3a shows, for example, the plan view bright field (BF) TEM image for a gold film on a Si(111) substrate; the dark areas are the gold deposits, whereas the lighter areas correspond to the silicon substrate. To investigate the orientation of the gold layer with respect to the underlying silicon

JANO

Figure 2. Scanning electron micrographs and transmission electron micrographs for gold galvanically displaced on silicon surfaces. (a and b) Plan view and cross-section SEM images of Au films on Si(111) formed from 0.1 mM KAuCl<sub>4</sub> (aq) and 1% HF (aq) for 7.5 min. (c and d) Plan view and cross-section SEM images of Au films on Si(100), formed from 0.1 mM KAuCl<sub>4</sub> (aq) and 1% HF (aq) for 7.5 min. (e) SEM image of silicon nanowires functionalized with gold nanoparticles. Conditions: 1 mM KAuCl<sub>4</sub> (aq) and 1% HF (aq) for 30 s. (f) TEM image for gold nanoparticles on a silicon nanowire following removal of the Si nanowires in panel e from their substrate *via* sonication in 100% ethanol, followed by spotting the supernatant layer on a lacy-carbon grid. The inset shows HRTEM image of a Si nanowire with a single gold nanoparticle.

planes, low and high resolution TEM images were taken along the [ $\overline{1}12$ ] zone axis of silicon (Figure 3b,c). The Moiré-fringes of the gold layer on Si( $1\overline{1}1$ ) are visible. TEM images along the [ $\overline{1}23$ ] zone axis are similar and are shown in the Supporting Information. The fringe spacing *D*, measured from the marked area in Figure 3b, is 9.5 Å. To calculate the theoretical fringe spacing, *D*, the following equation is used:<sup>59</sup>

$$D = \frac{d_{\text{Si}\{111\}} d_{\text{Au}\{111\}}}{d_{\text{Si}\{111\}} - d_{\text{Au}\{111\}}}$$

(3)

where  $d_{Si(111)}$  (3.134 Å) and  $d_{Au(111)}$  (2.355 Å) are the interplanar spacings for the silicon {111} and gold {111} planes, respectively. On the basis of the lattice parameters of the gold and silicon {111} planes, *D* is calculated

to be 9.47 Å, identical within experimental error to the observed value of 9.5 Å. Therefore, the Moiré-fringes are parallel to both the gold and silicon planes. Such alignment is suggestive of an epitaxial relationship in which a single crystalline layer of gold is oriented in a parallel manner on the single crystalline Si(111),<sup>59–61</sup> as has been suggested for galvanic displacement of gold on silicon-based surface X-ray diffraction spectroscopy results.<sup>46</sup>

To confirm the epitaxial relationship between gold and silicon, selected area electron diffraction (SAED, beam size  $\approx$  100 nm) was taken along the [112] zone axis (Figure 3d). The silicon pattern consists of spots, due to its single crystal nature, arising from diffraction from the (111), (220), and (131) planes; gold shows dif-

www.acsnano.org

VOL. 3 • NO. 9 • 2809-2817 • 2009

2812

fraction from these same planes. Other features of note include the parallel feature of the {112} family of crystallographic planes, of both the silicon substrate and the gold overlayer. The gold (111) and (220) planes are parallel to the silicon  $(1\overline{1}1)$  and (220) planes, respectively: Au(111)//Si(111) and Au(110)//Si(110). Hence, the SAED pattern is strongly indicative of the Au(111) $[\bar{1}12]//$ Si(111)[112] in-plane epitaxial relationship of the goldon-silicon. Further investigation by XRD (Supporting Information) for thicker gold films on Si(111) immersed in 0.1 mM KAuCl<sub>4</sub> (ag) and 1% HF (ag) for 20 min showed gold peaks for only the (111) and (222) planes, indicating the single crystal nature of the gold overlayer and the preferential growth of the gold layer along the  $\langle 111 \rangle$  growth direction; the gold layer grew along the same crystallographic direction as the underlying substrate.

The phenomenon of heteroepitaxial crystallization involves the epitaxial growth of a layer (an epilayer) with a chemical composition and, typically, structural parameters different from those of the substrate.<sup>61</sup> Lattice mismatch or misfit (the disregistry of the interfacial atomic arrangement of the substrate and the overgrown epilayer) is known to have a significant effect on epitaxy.<sup>61</sup> Au(111) and Si(111) with interplanar d spacings of 2.355 and 3.134 Å, respectively, have about a 25% lattice mismatch. By considering the coincident site lattice interface (CSL), however, in which three silicon lattices match with four gold lattices,  $4xd_{Au(111)} = 9.420$  Å and  $3xd_{(Si(111))}$ = 9.402 Å, the lattice mismatch is only 0.2%. Such heteroepitaxy has previously been observed for evaporated gold on silicon following annealing at temperatures greater than 380 °C.<sup>62</sup> A CSL interface has been considered for the epitaxial growth of the electron-beam evaporated silver on Si(111) surfaces.63

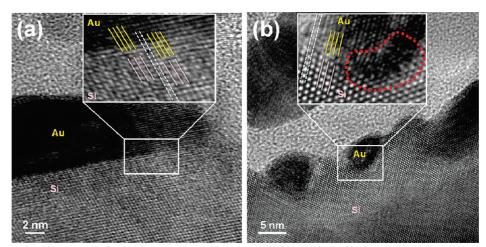

To visualize the gold nanoparticle—silicon interfaces of Au/ Si(111) and Au/Si(100) and confirm heteroepitaxy, crosssectional high resolution TEM (HRTEM) investigations were carried out. Figure 4a shows crosssectional HRTEM image for a gold nanocrystallite on Si(111) that reveals the coincidence of four gold lattice fringes with three silicon lattice fringes, as marked by the yellow and pink

lines, respectively. In addition, the top epitaxial gold planes are clearly parallel to the direction of those of the underlying silicon substrate. Similar results were observed for Au/Si(100) as shown in Figure 4b. In the case of gold on Si(100) (Figure 4b), the gold-silicon interface displays a significant degree of heterogeneity some areas have very clear coincident gold and silicon lattices, whereas others appear less ordered (Supporting Information). In the inset of Figure 4b, one ill-defined region is highlighted, the exact composition of which is asof-yet unknown (*vide infra*).

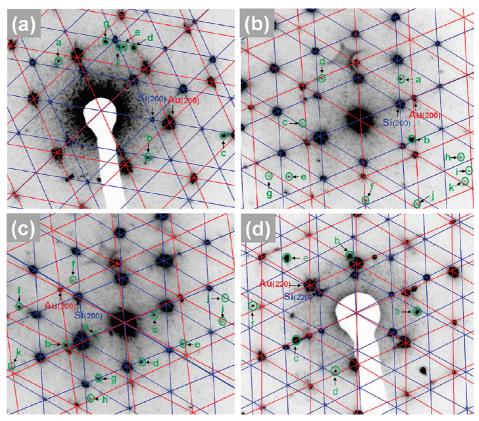

Because prior literature contains much postulation regarding the existence of intermetallics (gold—silicides),<sup>10,48</sup> nanobeam diffraction with a 20 nm probe was utilized to glean further information about the interface between a single gold nanocrystallite and Si(111) and Si(100) surfaces, and Si nanowires. As shown in Figure 5, the heteroepitaxial gold—silicon relationship is visible from the nanobeam diffraction patterns of all the cross-sectional gold—silicon interfaces. Alignment of gold and silicon diffraction spots, marked by red and blue lines, respectively, indicates that the growth of the crystalline gold is in the direction of the underlying silicon planes; both materials diffract along the same zone axes. In the case of Si(111) and Si(100), diffraction patterns were taken along the [110] zone axis, and the [111] for the nanowires.

There are, however, diffraction spots that do not correspond to either gold or silicon planes, and have interplanar spacings unrelated to the marked gold or silicon planes (red/blue lines), as indicated in green in Figure 5a-d. It is possible that the extra spots on Si(100)/gold result from the presence of crystalline gold silicides (summarized in Table 1, Supporting Information). In Figure 5a for gold on Si(111), there

Figure 4. Cross-sectional HRTEM images for gold-silicon interfaces, formed by immersing the substrates in 0.1 mM KAuCl<sub>4</sub> (aq) and 1% HF (aq) for 7.5 min: (a) Si(111), (b) Si(100). The yellow and pink lines show the coincident site lattice interfaces for the gold and silicon planes, respectively. The area in panel b outlined in red highlights an ill-defined region of the gold-silicon interface. Both images were taken close to the [110] zone axis. The white lines show the alignment and the parallel nature of the gold epilayer to the underlying silicon substrates.

are seven additional spots (in green), of which four can be indexed against the  $Au_2Si$ ,  $Au_5Si$ ,  $Au_7Si$  intermetallics. In Figure 5b for gold on Si(100), 11 additional spots are observed of which 9 can be indexed for intermetallics,

and in Figure 5c, for a different region of gold on Si(100), 12 extra spots are observed of which 7 can be indexed for intermetallics. The spots in the Si(100) case correspond to the following intermetallics: Au<sub>7</sub>Si, Au<sub>4</sub>Si, Au<sub>5</sub>Si, Au<sub>5</sub>Si<sub>2</sub>, Au<sub>3</sub>Si<sub>2</sub>, Au<sub>3</sub>Si, and Au<sub>2</sub>Si. Similarly, six extra spots are observed in the diffraction pattern for a gold nanoparticle on a silicon nanowire (Figure 5d), three of which can be indexed to the Au<sub>2</sub>Si, Au<sub>5</sub>Si, and Au<sub>7</sub>Si intermetallics. Because the nanoprobe diffraction studies are certainly not comprehensive with respect to determination and characterization of gold silicides due to the very high complexity of the system, the characterization of these gold silicides cannot be considered complete. We surmise that the intermetallics reside in the illdefined regions (vide supra, Figure 4b) since there is no evidence for involvement of foreign material in the Si/Au heteroepitaxial layers. The

therefore most likely composed of regions of heteroepitaxial gold-on-silicon, and separate domains containing an intermetallic sandwiched between the gold and silicon layers.

Figure 5. Nanobeam diffraction patterns (probe  $\approx$  20 nm) of gold-on-silicon samples. Blue and red lines correspond to silicon and gold planes, respectively. (a–c) Cross-sectioned gold-on-silicon wafers prepared through immersion of Si wafer shards in 0.1 mM KAuCl<sub>4</sub> (aq) + 1% HF (aq) for 7.5 min. Diffraction patterns were taken close to the [110] zone axis (a–c): (a) Si(111), (b,c) diffraction patterns for Si(100), taken at different locations. (d) Diffraction pattern, taken close to the [111] zone axis, from an interface between an individual gold nanoparticle and a silicon nanowire prepared using 1 mM KAuCl<sub>4</sub> (aq) and 1% HF (aq) for 30 s.

gold-silicon interfaces are

# ARTICLE

2814

Figure 5b,c, as stated earlier, shows the nanobeam diffraction patterns for gold nanoparticle-Si(100) interfaces from different locations. Figure 5c shows an area in which the gold planes are tilted by about  $\sim$  3.3° from the silicon planes. A 2.0° tilting was observed for Au planes on Si nanowires as well, Figure 5d. Crystallographic tilting of heteroepitaxial systems with their vicinal substrates is often observed;<sup>64</sup> for instance, tilting of heteroepitaxial gold and silver on silicon has been described previously,<sup>46,52,65-67</sup> and has been ascribed to misfit dislocation (disregistry of the epilayer and substrate planes),<sup>64,66,68</sup> or misfit between the height of a gold monolayer and a silicon step.<sup>67</sup> In the case of a silicon surface in an aqueous HF solution under galvanic displacement conditions, the surface will certainly not be flat, and thus surface roughness is most likely playing an important role in the observed epitaxial tilting, leading to defects and dislocations.

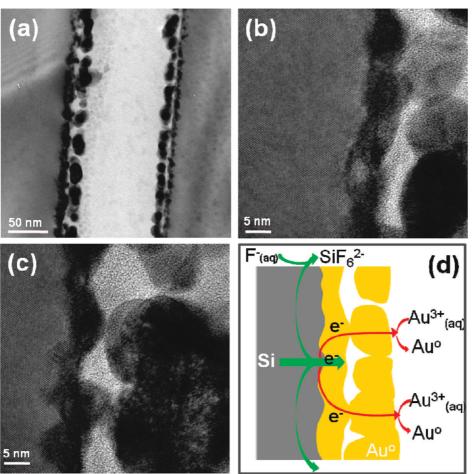

**Epitaxy Growth Mode.** For galvanic displacement of gold on silicon, two growth modes have been postulated to be in operation: the Stranski–Krastanov (SK) mode,<sup>48</sup> and Volmer–Weber (VW) growth.<sup>37,38,46,47</sup> The SK mode is common in lattice mismatched heteroepi-

taxial systems such as InAs on GaAs,<sup>69,70</sup> Ge on Si,<sup>71</sup> Ag on Si,<sup>72</sup> and Au on Si.48,73,74 In the SK growth mode, a twodimensional intermediate submonolayer forms and acts as a base for subsequent island growth.<sup>61</sup> Through their AFM studies of galvanic displacement of gold on silicon, Carraro and co-workers suggest surface morphology that is consistent with the SK mode of growth, in which the silicon surface is coated with a gold silicon silicide base monolayer, decorated with gold nanoparticles.<sup>48</sup> The SK mode was also postulated to be the growth mode for evaporated gold on Si(111) as judged via STM surface studies.73,74 A threedimensional (3D), island or Volmer-Weber (VW) growth mode has also been reported for the deposition of gold on silicon surfaces by galvanic displacement.37,38,46,47 VW growth mode involves the nucleation of small clusters directly on the substrate surface followed by their subsequent growth into islands.<sup>61</sup> For galvanically displaced gold on silicon, AFM studies along with sur-

face X-ray diffraction<sup>46</sup> and surface second harmonic generation<sup>37,38,47</sup> surface analyses reveal Au cluster formation which would be suggestive of a 3D or VW growth mechanism. To try to shed some light on the possible mechanism, detailed cross-sectional TEM imaging was employed, as shown in Figure 6 for Au/ Si(100); similar results for Si(111) are observed (Supporting Information). Two silicon wafers were immersed for 7.5 min in a solution of 0.1 mM KAuCl<sub>4</sub> (aq) and 1% HF (aq), followed by gluing them together with a  $\sim$ 100 nm layer of M-Bond and then microtomed to form a sandwich less than one micrometer thick (details in the experimental section). As can be seen in Figure 6a-c, there is a  $\sim$ 5 nm thick layer of gold (gold lattice planes are visible), closely allied with the silicon substrate, capped by an overlayer of necked gold particles. The high resolution TEM images (Figure 6b,c) show that the  $\sim$ 5 nm gold layer is formed by the coalescence of gold nanoparticles that presumably grew from the initially formed nuclei on the rough (on the nanoscale) silicon surface. The rough nature of this interface results in scattered nucleation events,<sup>21</sup> followed by growth of metallic gold until the metal deposits make contact

ARTICLE

with each other. The apparent overlayer of nanoparticle growth, above the initial gold-silicon contact, results from further deposition on the surface with longer immersion times in which the more closely siliconbonded gold acts as the cathodic layer through which electron transport takes place. These electrons, produced from the corrosion of the exposed silicon surface (perhaps nearby or distal),75-78 reduce gold ions in close vicinity in the solution to metallic gold, producing the necked particle overlayer. Figure 6d schematically illustrates a possible mechanism for the galvanic displacement process for gold on silicon, in which electrons from silicon dissolution promoted by fluoride ion lead to reduction of gold(III) complexes in the aqueous solution. The discrepancy between the observed results from different research groups most likely arises from the varying conditions used by each. If the conditions are such that deposition occurs on atomically flat hydride-terminated Si(111) planes, for instance, then an SK growth mode would be more likely. In our case, silicon surface roughening (on the nanoscale) is promoted by galvanic displacement,<sup>57</sup> and thus the VW growth appears to predominate, at least initially. The observed roughening of the interfaces during galvanic displacement is almost certainly the cause for VW island growth mode, and may also be the source of interfacial heterogeneity with respect to gold—silicon intermetallic formation, and heteroepitaxy.

### CONCLUSIONS

Galvanic displacement is a useful approach for synthesizing metal-on-semiconductor interfaces for a range of applications. Through detailed TEM and nanobeam diffraction studies of galvanic gold deposition on silicon [Si(100), Si(111) and silicon nanowires], a better understanding of the interface between the silicon and the metallic gold was achieved. A heteroepitaxial relationship between the gold and silicon was confirmed, and was directly observed by high resolution TEM on both single crystal silicon shards and the nanowires, revealing a coincident site lattice of four gold to three silicon lattices (lattice mismatch of 0.2%). Nanobeam diffraction patterns taken from a 20 nm gold-silicon interfacial area reveal a host of spurious spots that are clearly not derived from known gold or silicon planes, but are suggestive of gold-silicon intermetallics. Finally, cross-section TEM images of microtomed samples reveal a rough silicon interface and nucleated island growth of gold that is suggestive of Volmer-Weber growth, under these conditions.

### **EXPERIMENTAL SECTION**

**Generalities.** Unless otherwise noted, all experiments were performed under ambient laboratory conditions. Si(111) and Si(100) (p-type, B-doped,  $\rho < 0.005~\Omega\cdot$  cm, 500  $\mu$ m thickness) wafers were purchased from Silicon Quest International, Inc. KAuCl<sub>4</sub> · xH\_2O was purchased from Strem Chemicals. Anchored silicon nanowires were grown by the vapor liquid solid technique on a p-type (B-doped) Si(100) substrate.<sup>49,79</sup>

Pretreatment of Silicon Substrates. All wafers were diced into 1 cm<sup>2</sup> pieces with a diamond scriber. Silicon shards were degreased in a methanol ultrasonic bath for 15 min and dried under a nitrogen stream. The wafers were then cleaned using the following standard RCA cleaning procedures.<sup>16</sup> The wafers were first immersed into a hot solution of H<sub>2</sub>O:NH<sub>4</sub>OH:H<sub>2</sub>O<sub>2</sub> (5:1:1) for 15 min, and after rinsing with excess water, they were immersed into a hot solution of H2O:HCl:H2O2 (6:1:1) for 15 min. The wafers were again rinsed with excess water and then dried under a stream of nitrogen. Following this cleaning procedure, the wafers were immersed into 1% HF (aq) for 7 min, to remove the native surface oxide film. The samples were then rinsed with water and dried under a nitrogen stream. In the case of silicon nanowires, the wafer was divided into smaller pieces. Each substrate was cleaned by immersion in a mixture of  $H_2SO_4$ : $H_2O_2$  (ag) (1:1) for 5 min.<sup>49</sup> The samples were then rinsed with distilled water and dried under nitrogen. To hydrogen passivate the silicon nanowires, the substrates were immersed in 1% HF (aq) for 3 min, then rinsed with water and dried under nitrogen.

**Metal Deposition.** The silicon wafer shard was immersed in the desired aqueous gold salt and hydrofluoric acid solution in a Teflon beaker. The gold salt/acid solutions were prepared by mixing 0.1 mL of 0.01 M KAuCl<sub>4</sub> • *x*H<sub>2</sub>O and 9.9 mL of 1% HF (aq) for a given time. After metal deposition, the sample was thoroughly rinsed with water and dried under a nitrogen stream. In the case of silicon nanowires, a 10  $\mu$ L drop of 1 mM KAuCl<sub>4</sub> (aq) and 1% HF (aq) was placed on the nanowire-coated substrate surface for 30 s, then rinsed with distilled water and dried under nitrogen.<sup>49</sup>

Surface Characterization. The gold nanostructures on the silicon surfaces were characterized by scanning electron microscopy (SEM), transmission electron microscopy (TEM), and X-ray diffraction (XRD). SEM (Hitachi S-4800 FE-SEM) of gold nanostructures was typically performed with an electron energy of 20 keV. TEM images and nanobeam electron diffraction patterns, using a probe of about 20 nm, were recorded on a 200 kV JEOL 2200FS TEM/STEM instrument, equipped with a high tilt cryo-polepiece. X-ray diffraction was performed on a Bruker D8 Discover instrument equipped with a sealed Cu tube. The peaks in the X-ray diffraction pattern were identified in terms of the Bragg angle, 20.

TEM Sample Preparation. For cross-sectional samples of Si(111) and Si(100), six gold-silicon samples were glued together using M-Bond. A 3 mm cylinder was then cut from the side of the six wafers using an ultrasonic cutter and this cylinder was then inserted into a copper cylinder with epoxy. The copper tube was cut by a diamond saw into small disks about 600  $\mu m$  thick. Each disk was then polished on both sides to 100  $\mu$ m thickness. A  $\sim$ 1  $\mu$ m thickness was achieved by dimpling from both sides. For plan view samples, the backside of the silicon shard was mechanically polished until the silicon was thinned to less than a micrometer. After achieving submicrometer thicknesses for both cross-section and plan view samples, ion milling was then used to create a small hole and clean the surface. Milling was done at low temperature (less than -100 °C with LN<sub>2</sub> cooling) at 6° milling angle, and with a voltage/current of 5 kV/3 mA at the beginning, and 0.5 kV/3 mA for final polishing. In the case of silicon nanowires, the substrate was immersed into a vial with 100% ethanol and ultrasonicated for 5 min. A drop of the supernatant layer was then spotted onto a lacy-carbon grid.

Acknowledgment. This work was supported by NSERC, the National Research Council of Canada (NRC-NINT), the University of Alberta, the Canadian Foundation for Innovation (CFI), Alberta Ingenuity (Fellowship to S.Y.S.), and the Canada Research Chairs Program (CRC to J.M.B.). We are also thankful for the technical support at NINT and the Alberta Centre for Surface Engineering and Science (ACSES). We thank Dr. Brian Daly for the synthesis of the silicon nanowires and Sean McClure for his help in drawing the table of contents image. S.Y.S. thanks Cairo University, Egypt, for his leave of absence to perform his Ph.D. studies at the University of Alberta.

Supporting Information Available: Additional SEM and TEM data for gold-functionalized interfaces. This material is available free of charge via the Internet at http://pubs.acs.org.

## **REFERENCES AND NOTES**

- 1. Northrop, D. C. The Metal-Semiconductor Contact. *Nature* **1980**, *284*, 403–404.

- Leong, M.; Doris, B.; Kedzierski, J.; Rim, K.; Yang, M. Silicon Device Scaling to the Sub-10-nm Regime. *Science* 2004, 306, 2057–2060.

- Wu, Y.; Xiang, J.; Yang, C.; Lu, W.; Lieber, C. M. Single-Crystal Metallic Nanowires and Metal/Semiconductor Nanowire Heterostructures. *Nature* 2004, 430, 61–65.

- Li, B.; Luo, Z. Q.; Shi, L.; Zhou, J. P.; Rabenberg, L.; Ho, P. S.; Allen, R. A.; Cresswell, M. W. Controlled Formation and Resistivity Scaling of Nickel Silicide Nanolines. *Nanotechnology* **2009**, *20*, 1–7.

- Ootsuka, T.; Liu, Z. X.; Osamura, M.; Fukuzawa, Y.; Otogawa, N.; Nakayama, Y.; Tanoue, H.; Makita, Y. Beta-Fesi<sub>2</sub> Based Metal-Insulator-Semiconductor Devices Formed by Sputtering for Optoelectronic Applications. *Mater. Sci. Eng.*, B 2005, 124, 449–452.

- 6. Giziewicz, W. P.; Fonstad, C. G. Optoelectronic Integration Using Aligned Metal-to-Semiconductor Bonding. *J. Vac. Sci. Technol., A* **2002**, *20*, 1052–1056.

- Mokari, T.; Rothenberg, E.; Popov, I.; Costi, R.; Banin, U. Selective Growth of Metal Tips onto Semiconductor Quantum Rods and Tetrapods. *Science* 2004, *304*, 1787–1790.

- Lin, K. W.; Chen, H. I.; Lu, C. T.; Tsai, Y. Y.; Chuang, H. M.; Chen, C. Y.; Liu, W. C. A Hydrogen Sensing Pd/InGaP Metal-Semiconductor (MS) Schottky Diode Hydrogen Sensor. *Semicond. Sci. Technol.* 2003, *18*, 615–619.

- Brenner, A.; Riddell, G. E. Nickel Plating on Steel by Chemical Reduction. J. Res. Natl. Bur. Stand. 1946, 37, 31–34.

- Zhao, L. Y.; Siu, A. C. L.; Petrus, J. A.; He, Z. H.; Leung, K. T. Interfacial Bonding of Gold Nanoparticles on a H-Terminated Si(100) Substrate Obtained by Electro- and Electroless Deposition. J. Am. Chem. Soc. 2007, 129, 5730– 5734.

- San Paulo, A.; Arellano, N.; Plaza, J. A.; He, R. R.; Carraro, C.; Maboudian, R.; Howe, R. T.; Bokor, J.; Yang, P. D. Suspended Mechanical Structures Based on Elastic Silicon Nanowire Arrays. *Nano Lett.* **2007**, *7*, 1100–1104.

- daRosa, C. P.; Maboudian, R.; Iglesia, E. Copper Deposition onto Silicon by Galvanic Displacement: Effect of Silicon Dissolution Rate. J. Electrochem. Soc. 2008, 155, E70–E78.

- Carraro, C.; Maboudian, R.; Magagnin, L. Metallization and Nanostructuring of Semiconductor Surfaces by Galvanic Displacement Processes. Surf. Sci. Rep. 2007, 62, 499–525.

- Magagnin, L.; Maboudian, R.; Carraro, C. Gold Deposition by Galvanic Displacement on Semiconductor Surfaces: Effect of Substrate on Adhesion. *J. Phys. Chem. B* 2002, 106, 401–407.

- Aizawa, M.; Buriak, J. M. Block Copolymer Templated Chemistry for the Formation of Metallic Nanoparticle Arrays on Semiconductor Surfaces. *Chem. Mater.* 2007, 19, 5090–5101.

- Aizawa, M.; Buriak, J. M. Nanoscale Patterning of Two Metals on Silicon Surfaces Using an ABC Triblock Copolymer Template. J. Am. Chem. Soc. 2006, 128, 5877–5886.

- 17. Aizawa, M.; Buriak, J. M. Block Copolymer-Templated Chemistry on Si, Ge, InP, and GaAs Surfaces. J. Am. Chem. Soc. **2005**, *127*, 8932–8933.

- Aizawa, M.; Cooper, A. M.; Malac, M.; Buriak, J. M. Silver Nano-Inukshuks on Germanium. *Nano Lett.* 2005, *5*, 815–819.

- Nezhad, M. R. H.; Aizawa, M.; Porter, L. A.; Ribbe, A. E.; Buriak, J. M. Synthesis and Patterning of Gold Nanostructures on InP and GaAs *via* Galvanic Displacement. *Small* **2005**, *1*, 1076–1081.

VOL. 3 • NO. 9 • SAYED ET AL.

- Porter, L. A.; Choi, H. C.; Ribbe, A. E.; Buriak, J. M. Controlled Electroless Deposition of Noble Metal Nanoparticle Films on Germanium Surfaces. *Nano Lett.* **2002**, *2*, 1067–1071.

- Niwa, D.; Homma, T.; Osaka, T. Deposition Mechanism of Ni on Si(100) Surfaces in Aqueous Alkaline Solution. J. Phys. Chem. B 2004, 108, 9900–9904.

- Gorostiza, P.; Allongue, P.; Diaz, R.; Morante, J. R.; Sanz, F. Electrochemical Characterization of the Open-Circuit Deposition of Platinum on Silicon from Fluoride Solutions. *J. Phys. Chem. B* **2003**, *107*, 6454–6461.

- Sun, Y. G.; Wiederrecht, G. P. Surfactantless Synthesis of Silver Nanoplates and Their Application in SERS. *Small* 2007, 3, 1964–1975.

- Sun, X. H.; Wong, N. B.; Li, C. P.; Lee, S. T.; Kim, P. S. G.; Sham, T. K. Reductive Self-Assembling of Pd and Rh Nanoparticles on Silicon Nanowire Templates. *Chem. Mater.* 2004, *16*, 1143–1152.

- Bhuvana, T.; Kulkarni, G. U. Optimizing Growth Conditions for Electroless Deposition of Au Films on Si(111) Substrates. *Bull. Mater. Sci.* 2006, 29, 505–511.

- Jing, F.; Tong, H.; Kong, L.; Wang, C. Electroless Gold Deposition on Silicon(100) Wafer Based on a Seed Layer of Silver. *Appl. Phys. A* 2005, *80*, 597–600.

- Ye, X. R.; Wai, C. M.; Zhang, D. Q.; Kranov, Y.; McIlroy, D. N.; Lin, Y. H.; Engelhard, M. Immersion Deposition of Metal Films on Silicon and Germanium Substrates in Supercritical Carbon Dioxide. *Chem. Mater.* **2003**, *15*, 83–91.

- Miyake, H.; Ye, S.; Osawa, M. Electroless Deposition of Gold Thin Films on Silicon for Surface-Enhanced Infrared Spectroelectrochemistry. *Electrochem. Commun.* 2002, 4, 973–977.

- Li, H. H.; Liang, C. L.; Liu, M.; Zhong, K.; Tong, Y. X.; Liu, P.; Hope, G. A. Synthesis of Indium Nanowires by Galvanic Displacement and their Optical Properties. *Nanoscale Res. Lett.* 2009, *4*, 47–53.

- Lv, S.; Suo, H.; Zhou, T. L.; Wang, C. X.; Jing, S. Y.; Fu, Q. B.; Xu, Y. A.; Zhao, C. Effect of Synthesis Route on the Morphologies of Silver Nanostructures by Galvanic Displacement Reaction. *Solid State Commun.* **2009**, *149*, 227–230.

- Darosa, C. P.; Iglesia, E.; Maboudian, R. Dynamics of Copper Deposition onto Silicon by Galvanic Displacement. J. Electrochem. Soc. 2008, 155, D244–D250.

- Gao, D.; He, R. R.; Carraro, C.; Howe, R. T.; Yang, P. D.; Maboudian, R. Selective Growth of Si Nanowire Arrays via Galvanic Displacement Processes in Water-in-Oil Microemulsions. J. Am. Chem. Soc. 2005, 127, 4574–4575.

- Magagnin, L.; Bertani, V.; Cavallotti, P. L.; Maboudian, R.; Carraro, C. Selective Deposition of Gold Nanoclusters on Silicon by a Galvanic Displacement Process. *Microelectron. Eng.* 2002, *64*, 479–485.

- Niwa, D.; Homma, T.; Osaka, T. Deposition Behavior of Ni on Si(100) Surfaces in an Aqueous Alkaline Solution. J. Electrochem. Soc. 2005, 152, C54–C59.

- Lin, H. H.; Mock, J.; Smith, D.; Gao, T.; Sailor, M. J. Surface-Enhanced Raman Scattering from Silver-Plated Porous Silicon. J. Phys. Chem. B 2004, 108, 11654–11659.

- Kim, C.; Oikawa, Y.; Shin, J.; Ozaki, H. Co-Dot-Array Formation along Scratches on Si(111) Surface by Electroless Deposition. *Microelectron. J.* 2003, 34, 607–609.

- Srinivasan, R.; Suni, I. I. Electroless Deposition of Au onto Si(111) Studied by Surface Second Harmonic Generation. Surf. Sci. 1998, 408, L698–L702.

- Srinivasan, R.; Suni, I. I. Kinetic Analysis of Au Deposition from Aqueous HF onto Si(111) by Surface Second Harmonic Generation. J. Electrochem. Soc. 1999, 146, 570– 573.

- Peng, K. Q.; Zhu, J. Simultaneous Gold Deposition and Formation of Silicon Nanowire Arrays. J. Electroanal. Chem. 2003, 558, 35–39.

- Weller, R. A.; Ryle, W. T.; Newton, A. T.; McMahon, M. D.; Miller, T. M.; Magruder, R. H. A Technique for Producing Ordered Arrays of Metallic Nanoclusters by Electroless Deposition in Focused Ion Beam Patterns. *IEEE Trans. Nanotechnol.* 2003, *2*, 154–157.

- Sugimura, H.; Nakagiri, N. Scanning Probe Anodization— Patterning of Hydrogen-Terminated Silicon Surfaces for the Nanofabrication of Gold Structures by Electroless Plating. J. Vac. Sci. Technol., B 1995, 13, 1933–1937.

- Oskam, G.; Long, J. G.; Natarajan, A.; Searson, P. C. Electrochemical Deposition of Metals onto Silicon. J. Phys. D: Appl. Phys. **1998**, 31, 1927–1949.

- Sayed, S. Y.; Daly, B.; Buriak, J. M. Characterization of the Interface of Gold and Silver Nanostructures on InP and GaAs Synthesized via Galvanic Displacement. J. Phys. Chem. C 2008, 112, 12291–12298.

- Doerk, G. S.; Ferralis, N.; Carraro, C.; Maboudian, R. Growth of Branching Si Nanowires Seeded by Au–Si Surface Migration. J. Mater. Chem. 2008, 18, 5376–5381.

- Yasseri, A. A.; Sharma, S.; Jung, G. Y.; Kamins, T. I. Electroless Deposition of Au Nanocrystals on Si(111) Surfaces as Catalysts for Epitaxial Growth of Si Nanowires. *Electrochem. Solid-Sate Lett.* **2006**, *9*, C185–C188.

- Warren, S.; Reitzle, A.; Kazimirov, A.; Ziegler, J. C.; Bunk, O.; Cao, L. X.; Renner, F. U.; Kolb, D. M.; Bedzyk, M. J.; Zegenhagen, J. A Structure Study of the Electroless Deposition of Au on Si(111):H. Surf. Sci. 2002, 496, 287–298.

- Rossiter, C.; Suni, I. I. Atomic Force Microscopy of Au Deposition from Aqueous HF onto Si(111). *Surf. Sci.* 1999, 430, L553–L557.

- Ferralis, N.; Maboudian, R.; Carraro, C. Structure and Morphology of Annealed Gold Films Galvanically Displaced on the Si(111) Surface. J. Phys. Chem. C 2007, 111, 7508–7513.

- Yasseri, A. A.; Sharma, S.; Kamins, T. I.; Li, Z.; Williams, R. S. Growth and Use of Metal Nanocrystal Assemblies on High-Density Silicon Nanowires Formed by Chemical Vapor Deposition. *Appl. Phys. A* **2006**, *82*, 659–664.

- Zhang, J. G.; Gao, Y.; Hanrath, T.; Korgel, B. A.; Buriak, J. M. Block Copolymer Mediated Deposition of Metal Nanoparticles on Germanium Nanowires. *Chem. Commun.* 2007, 1438–1440.

- Magagnin, L.; Maboudian, R.; Carraro, C. Selective Deposition of Thin Copper Films onto Silicon with Improved Adhesion. *Electrochem. Solid-Sate Lett.* 2001, 4, C5–C7.

- Piscopiello, E.; Tapfer, L.; Antisari, M. V.; Paiano, P.; Prete, P.; Lovergine, N. Formation of Epitaxial Gold Nanoislands on (100) Silicon. *Phys. Rev. B* **2008**, *78*, 035305.

- Sato, K.; Huang, W. J.; Bohra, F.; Sivaramakrishnan, S.; Tedjasaputra, A. P.; Zuo, J. M. Size-Dependent Structural Transition from Multiple-Twinned Particles to Epitaxial fcc Nanocrystals and Nanocrystal Decay. *Phys. Rev. B* 2007, 76, 144113-1–144113-8.

- Arakaki, H.; Ohashi, K.; Sudou, T. Sputter-Induced Defects in Zn-Doped GaAs Schottky Diodes. *Semicond. Sci. Technol.* 2004, 19, 127–132.

- Shimizu, T.; Xie, T.; Nishikawa, J.; Shingubara, S.; Senz, S.; Gösele, U. Synthesis of Vertical High-Density Epitaxial Si(100) Nanowire Arrays on a Si(100) Substrate Using an Anodic Aluminum Oxide Template. *Adv. Mater.* 2007, *19*, 917–920.

- Shimizu, T.; Senz, S.; Shingubara, S.; Gösele, U. Synthesis of Epitaxial Si(100) Nanowires on Si(100) Substrate Using Vapor–Liquid–Solid Growth in Anodic Aluminum Oxide Nanopore Arrays. *Appl. Phys. A* **2007**, *87*, 607–610.

- Porter, L. A.; Choi, H. C.; Schmeltzer, J. M.; Ribbe, A. E.; Elliott, L. C. C.; Buriak, J. M. Electroless Nanoparticle Film Deposition Compatible with Photolithography, Microcontact Printing and Dip-Pen Nanolithography Patterning Technologies. *Nano Lett.* **2002**, *2*, 1369–1372.

- Hochbaum, A. I.; Chen, R. K.; Delgado, R. D.; Liang, W. J.; Garnett, E. C.; Najarian, M.; Majumdar, A.; Yang, P. D. Enhanced Thermoelectric Performance of Rough Silicon Nanowires. *Nature* 2008, 451, 163–U5.

- De Graef, M., Intoduction to Conventional Transmission Electron Microscopy; Cambridge University Press: New York, 2003; p 530–535.

- Pashley, D. W.; Stowell, M. J.; Jacobs, M. H.; Law, T. J. The Growth and Structure of Gold and Silver Deposits Formed by Evaporation Inside an Electron Microscope. *Philos. Mag.* 1964, 10, 127–158.

- Herman, M. A., Richter, W. Sitter, H. Epitaxy; Physical Principles and Technical Implementation; Springer: New York, 2004.

- Yokota, Y.; Hashimoto, H.; Saito, N.; Endoh, H. Electron-Microscope Observation of Au/Si (111) Interface in Atomic Level. Jpn. J. Appl. Phys. **1986**, 25, L168–L170.

- Li, B. Q.; Zuo, J. M. The Development of Epitaxy of Nanoclusters on Lattice-Mismatched Substrates: Ag on H-Si(111) Surfaces. *Surf. Sci.* 2002, *520*, 7–17.

- Ayers, J. E.; Ghandhi, S. K.; Schowalter, L. J. Crystallographic Tilting of Heteroepitaxial Layers. J. Cryst. Growth 1991, 113, 430–440.

- 65. Sugihara, S.; Okazaki, K.; Suganuma, K. Wetting of Silicon Single-Crystal by Silver and Tin, and Their Interfaces. *J. Mater. Sci.* **1993**, *28*, 2455–2458.

- Legoues, F. K.; Liehr, M.; Renier, M.; Krakow, W. Microstructure of Epitaxial Ag/Si(111) and Ag/Si(100) Interfaces. *Philos. Mag. B.* **1988**, *57*, 179–189.

- Munford, M. L.; Maroun, F.; Cortes, R.; Allongue, P.; Pasa, A. A. Electrochemical Growth of Gold on Well-Defined Vicinal H-Si(111) Surfaces Studied by AFM and XRD. *Surf. Sci.* 2003, *537*, 95–112.

- Sundaravel, B.; Das, A. K.; Ghose, S. K.; Sekar, K.; Dev, B. N. Epitaxial Growth of Silver on Br-Passivated Si(111) Substrates under High Vacuum. *Appl. Surf. Sci.* **1999**, *137*, 11–19.

- Karrai, K.; Warburton, R. J.; Schulhauser, C.; Hogele, A.; Urbaszek, B.; McGhee, E. J.; Govorov, A. O.; Garcia, J. M.; Gerardot, B. D.; Petroff, P. M. Hybridization of Electronic States in Quantum Dots Through Photon Emission. *Nature* 2004, *427*, 135–138.

- Bimberg, D.; Grundmann, M.; Ledentsov, N. N.; Ruvimov, S. S.; Werner, P.; Richter, U.; Heydenreich, J.; Ustinov, V. M.; Kopev, P. S.; Alferov, Z. I. Self-Organization Processes in MBE-Grown Quantum Dot Structures. *Thin Solid Films* 1995, 267, 32–36.

- Hansson, P. O.; Albrecht, M.; Dorsch, W.; Strunk, H. P.; Bauser, E. Interfacial Energies Providing a Driving-Force for Ge/Si Heteroepitaxy. *Phys. Rev. Lett.* **1994**, *73*, 444–447.

- 72. Glueckstein, J. C.; Evans, M. M. R.; Nogami, J. Surface Unwetting During Growth of Ag on Si(001). *Phys. Rev. B* **1996**, *54*, 11066–11069.

- Rota, A.; Martinez-Gil, A.; Agnus, G.; Moyen, E.; Maroutian, T.; Bartenlian, B.; Megy, R.; Hanbucken, M.; Beauvillain, P. Au Island Growth on a Si(111) Vicinal Surface. *Surf. Sci.* 2006, 600, 1207–1212.

- Kirakosian, A.; Lin, J. L.; Petrovykh, D. Y.; Crain, J. N.; Himpsel, F. J. Functionalization of Silicon Step Arrays I: Au Passivation of Stepped Si(111) Templates. *Appl. Phys.* 2001, 90, 3286–3290.

- Torcheux, L.; Mayeux, A.; Chemla, M. Electrochemical Coupling Effects on the Corrosion of Silicon Samples in HF Solutions. J. Electrochem. Soc. 1995, 142, 2037–2046.

- Hon, M.; DelRio, F. W.; White, J. T.; Kendig, M.; Carraro, C.; Maboudian, R. Cathodic Corrosion of Polycrystalline Silicon MEMS. *Sens. Actuators, A* **2008**, *145*, 323–329.

- Pierron, O. N.; Macdonald, D. D.; Muhlstein, C. L. Galvanic Effects in Si-Based Microelectromechanical Systems: Thick Oxide Formation and its Implications for Fatigue Reliability. *Appl. Phys. Lett.* **2005**, 86.

- Miller, D. C.; Gall, K.; Stoldt, C. R. Galvanic Corrosion of Miniaturized Polysilicon Structures Morphological, Electrical, and Mechanical Effects. *Electrochem. Solid-Sate Lett.* 2005, 8, G223–G226.

- Sharma, S.; Kamins, T. I.; Williams, R. S. Synthesis of Thin Silicon Nanowires Using Gold-Catalyzed Chemical Vapor Deposition. *Appl. Phys. A: Mater.* 2005, *80*, 1225–1229.